ОСЦИЛЛОГРАФЫ. ВЕРТИКАЛЬНОЕ РАЗРЕШЕНИЕ. ЧТО ЭТО? ЧАСТЬ 4

Магазин Gtest(R) предлагает

широкую номенклатуру Осциллографов

на приводимой страничке сайта в самом конце настоящего Раздела, а также рекомендуемые приборы и статьи для

самообразования

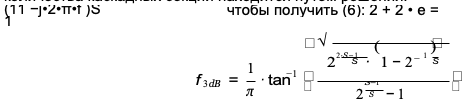

Ширина полосы пропускания по уровню 3 дБ как доля частоты Найквиста такого количества каскадных секций находится путем решения:

Улучшение бит для некоторого количества этапов показано в Таблице 1. На практике нам не нравится иметь дробные улучшения бит, поэтому вместо каскадирования усредняющих этапов мы находим дробное значение S, которое обеспечивает желаемое улучшение бит, и просто находим фильтр, который соответствует отклику. Таким образом, битовые улучшения и количество стадий для этих улучшений сведены в Таблицу 2. Когда фильтры ERES вычисляются, мы обнаруживаем, что нам нужно очень большое количество стадий и, следовательно, очень длинные фильтры. На практике большинство коэффициентов фильтра незначительны, поскольку большое количество каскадов лучше приближает истинную гауссову форму, и мы знаем, что хвосты гауссовской функции, как правило, имеют очень малые значения. Эти отклики фильтра показаны во временной области на Рисунке 5 и в частотной области на Рисунке 6 (см. ОСЦИЛЛОГРАФЫ. ВЕРТИКАЛЬНОЕ РАЗРЕШЕНИЕ. ЧТО ЭТО? ЧАСТЬ 3).

| Этапы | 1 2•S ( ω ) • ´ 2•π cos • dω 2•π 0 2 | Улучшение битов | Пропускная способность (доля скорости Найквиста) |

| 1 | 1 2 | 0.5 | 0.5 |

| 2 | 3 8 | 0.708 | 0.364 |

| 3 | 5 16 | 0.839 | 0.3 |

| 4 | 35 128 | 0.935 | 0.261 |

| 5 | 63 256 | 1.011 | 0.234 |

| 6 | 231 1024 | 1.074 | 0.214 |

| 7 | 429 2048 | 1.128 | 0.199 |

Таблица 1 - Улучшение битов ERES в зависимости от этапов

| Этапы | 1 2•S ( ω ) • ´ 2•π cos • dω 2•π 0 2 | Улучшение битов | Пропускная способность (доля скорости Найквиста) |

| 1 | 1 2 | 0.5 | 0.5 |

| 2 | 1 4 | 1 | 0.238 |

| 3 | 1 8 | 1.5 | 0.118 |

| 4 | 1 16 | 2 | 0.059 |

| 5 | 1 32 | 2.5 | 0.029 |

| 6 | 1 64 | 3 | 0.015 |

| 7 | 1 128 | 3.5 | 0.007 |

Таблица 2 - Улучшения бит ERES с шагом 0,5 бита

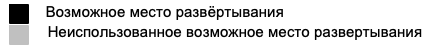

Рисунок 7 - Стандарт 40 ГЦ/с, восьмибитное временное чередование

Временное и вертикальное чередование

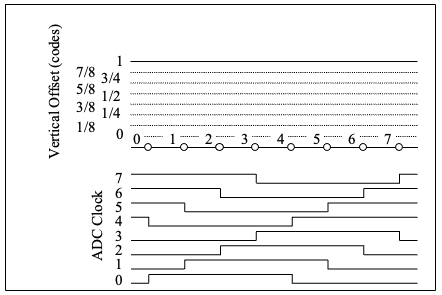

В этом разделе будут обсуждаться некоторые стратегии развертывания АЦП для улучшения разрешения. Чаще всего АЦП развертываются в схеме с временным чередованием для улучшения частоты дискретизации и устранения практических ограничений скорости отдельных АЦП. На рисунке 7 мы видим типичную ситуацию объединения АЦП для временного чередования. Здесь у нас есть восемь АЦП 5 Гвыб/с, расположенных таким образом, что их тактовые частоты выборки 5 ГГц задерживаются на долю фазы выборки 5 ГГц. Каждый АЦП смещен на одинаковую величину. Выборки АЦП 0 с заданной частотой выборки, выборки АЦП 1 на одну восьмую периода позже, выборки АЦП 2 на одну четверть периода выборки позже и т. д. После того, как данные получены, данные из данных каждого АЦП объединяются вместе в надлежащем временном порядке, образуя эффективное получение 40 Гвыб/с.

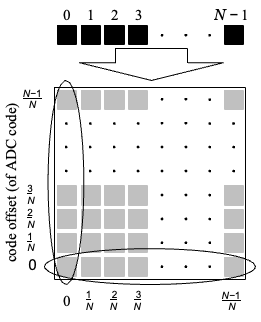

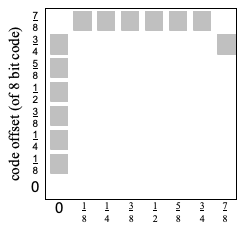

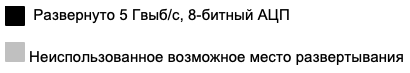

В рамках подготовки к последующему обсуждению на рисунке 8 мы показываем концептуальную схему размещения N АЦП как по времени, так и по смещению. Здесь у нас есть N 2 возможных мест развертывания для N АЦП. Любой из N АЦП может быть размещен в любом из мест (даже перекрываясь) смещенным на кратные 1/N восьмибитного кода по вертикали или индивидуального периода выборки АЦП по горизонтали. Традиционная схема с временным чередованием, проиллюстрированная на рисунке 7, показана с использованием этой концептуальной схемы на рисунке 9.

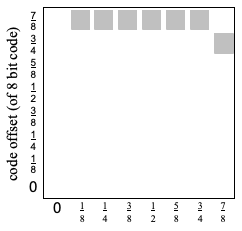

В то время как восемь АЦП, все размещенные в схеме с временным чередованием, являются одной крайностью, которая обеспечивает максимальную частоту выборки 40 Гвыб/с, но ограничены восьмибитным разрешением каждого АЦП, на рисунке 10 показана противоположная крайность. В этой компоновке все восемь АЦП выполняют выборку одновременно, но каждый смещен на одну восьмую кода. Это дает в результате 5 Гвыб/с захвата, который может обеспечить восемь уровней между каждым из восьми битовых кодов, тем самым расширяя разрешение до одиннадцати бит, хотя и с серьезным снижением частоты дискретизации.

Рисунок 8 - Концептуальные места развертывания ADC. Фаза выборки (тактовой частоты выборки АЦП)

Рисунок 9 - Концептуальное 40 Гбит/с, восьми битное временное чередование. Фаза выборки (5 ГГ/с тактовой частоты выборки)

Рисунок 10 - Концептуальное 5 Гвыб/с, одиннадцатибитное вертикальное чередование. Фаза выборки (5 ГГ/с тактовой частоты выборки)

Мы показали здесь, что существует компромисс, который может быть достигнут в том, как ресурсы АЦП используются между частотой дискретизации и разрешением. Важно понимать, как этот компромисс может быть рассмотрен.

Магазин Gtest® - авторизованный поставщик осциллографов в Украину: https://gtest.com.ua/izmeritelnye-pribory/ostcillografy

ПРОДОЛЖЕНИЕ СЛЕДУЕТ…